IC(부품) 품질 수준을 개선한다고 HBM이나 CDM specification을 높이자고 제안하는 회사가 많다.

특히 SET 업체가 요청하는 경우가 있는데, 앞에서 포스팅 했듯이 SET ESD level 부품 ESD level은 전혀 다르다.

HBM과 CDM 은 IC 제조나, package 조립단계에서 handling을 잘 못해서 발생하는 불량을 모델링한 평가 방법이다.

IC가 set에 장착됐을때는 SET ESD 평가 방법(61000-4-5)으로 ESD robustness를 평가해야한다.

즉 ,부품 자체 ESD level이 높인다고 해서 SET level ESD(Module level ESD 포함)가 개선되지 않는다.

또한 제조 단계에서 나올 수 있는 불량을 막기 위해서 부품의 ESD specification만 올릴것이 아니라 라인의 ESD control도 병행해 개선해야 한다.

지난 2014년 JEDEC내 ESD industry council에서 논의한 내용이 있어 소개한다.

아래 내용을 이해하기 쉽게 정리했다.

https://www.jedec.org/sites/default/files/IndustryCouncil_CDM_January2014_JEDECversionMay2014.pdf

목적

회로 동작 속도는 높아지고, 크기는 증가하는 조건에서 현재 CDM level(500V 이상) 을 충족시키는 건 점점 어려워지고 있습니다.

본연구는 CDM 레벨이 500V 이하인 IC 가, 제조환경에서 사용가능한 ESD 제어 방법으로 안전하게 다뤄(생산) 질 수 있다는걸 보여 줍니다.

실제 산업영역에서의 조사와 제약 조건을 바탕으로 한 이번 연구를 통해 , 250V가 실용적인 CDM 목표 수준이라는걸 알 수 있습니다.

목차

CDM 관련사항

CDM 기술 및 설계 이슈

CDM Qualification 방법

CDM 보호를 위한 ESD 제어 방법

현장에서 발생한 불량 분석

요약

결론

로드맵

CDM 관련 사항

-CDM은 IC ESD testing을 위한 유일하고 중요한 평가방법 입니다.

-높은 peak current가 빠르게 방전하면서 심각한 IC 불량이 시장에서 발생합니다. 이런 불량은 HBM(또는 MM)에서 재현할 수 없습니다.

-CDM test는 이런 불량을 효과적으로 재현할 수 있습니다.

-전형적인 방전 시나리오(CDM)는 IC 테스트에서 시뮬레이팅 되고, 제조과정에서 이런 불량이 관찰 되었습니다.

-CDM은 필요하고 중요한 신뢰성 시험(Qualification test)입니다.

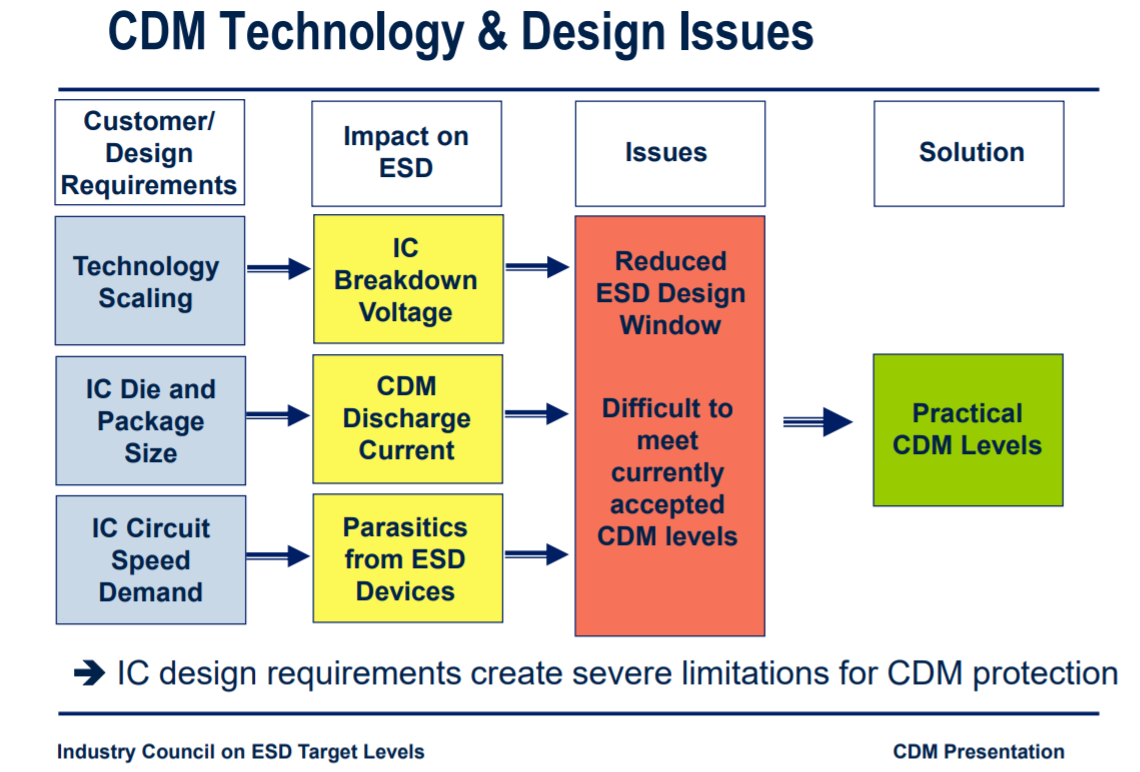

CDM 기술 및 설계 이슈

CDM 보호설계는

필요한(목표) CDM 전압이 IC 패키지에서 전류로 방전 한다는 모델을 기반으로 진행됩니다.

같은 CDM stress 전압 이라도 큰 패키지 size(capacitance) 에서는 discharge 전류가 증가 됩니다.

게다가, 공정이 미세해 짐에따라 gate와 juctions breakdown 전압은 낮아지고 있어 CDM 보호설계는 점점 어려워 지고 있습니다.

그림으로 표현하면 아래와 같습니다.

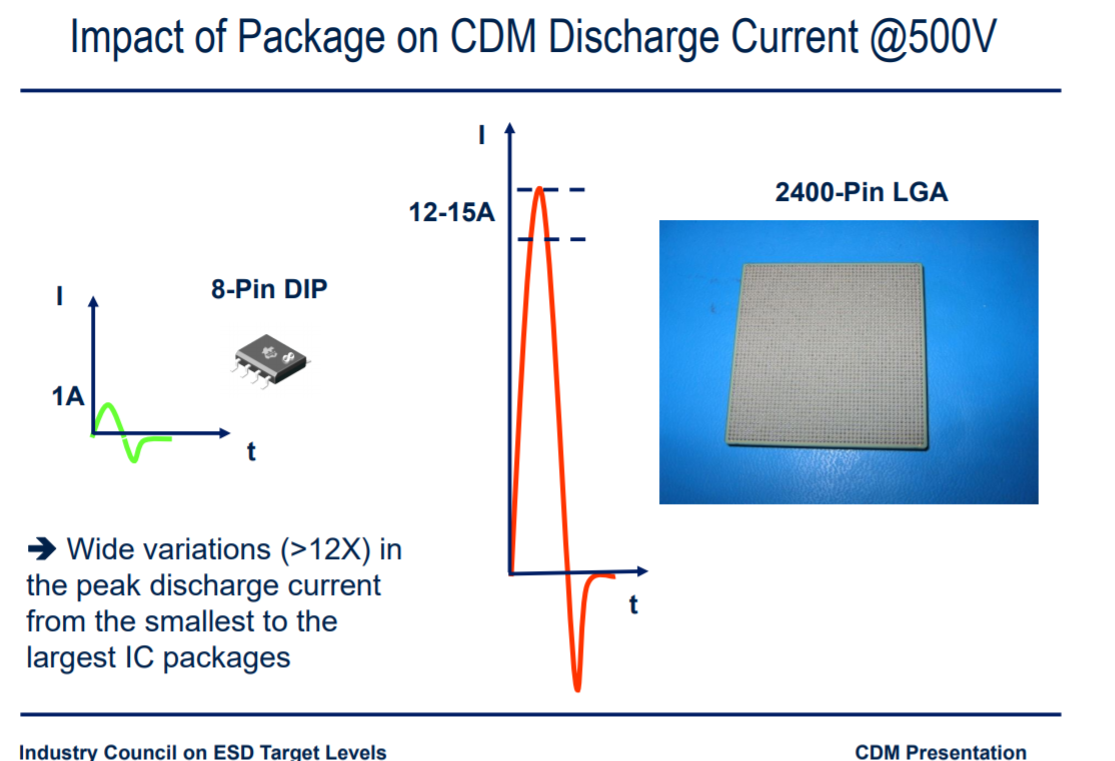

아래 그림처럼

같은 CDM 500V에서도 작은 패키지와 큰 패키지의 방전 전류는 12배 차이가 납니다.

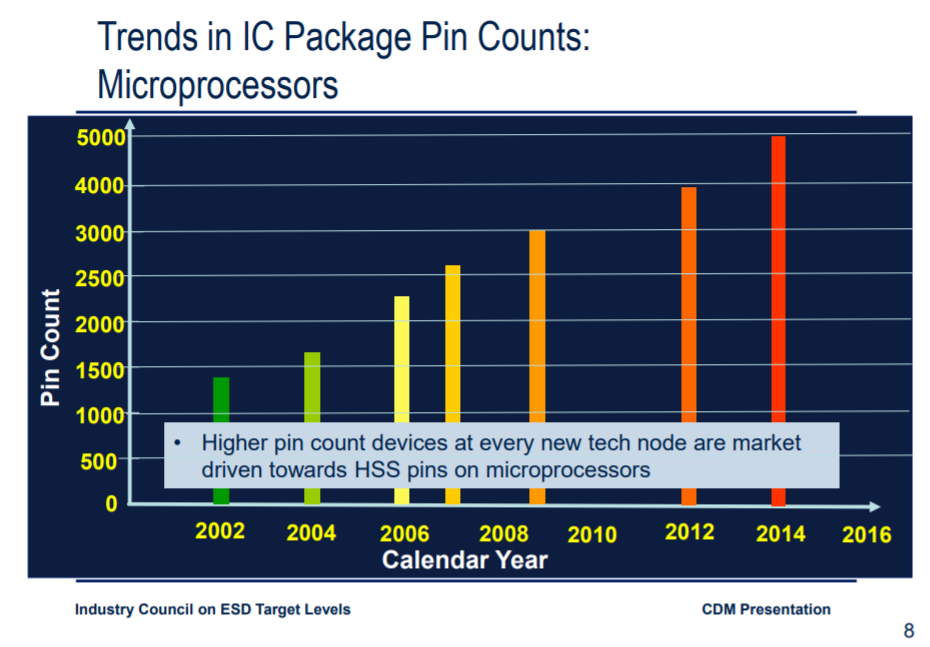

마이크로프로세서의 pin 증가추세 입니다.

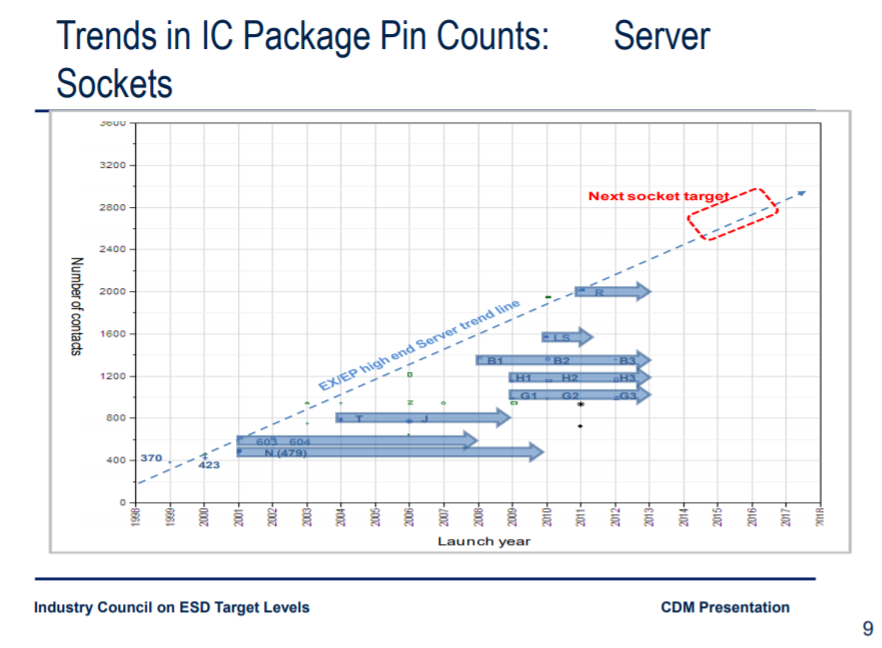

서버소켓의 pin 증가 추세 입니다.

CDM 500V 에서 pin 증가에 따른 peak current 입니다.

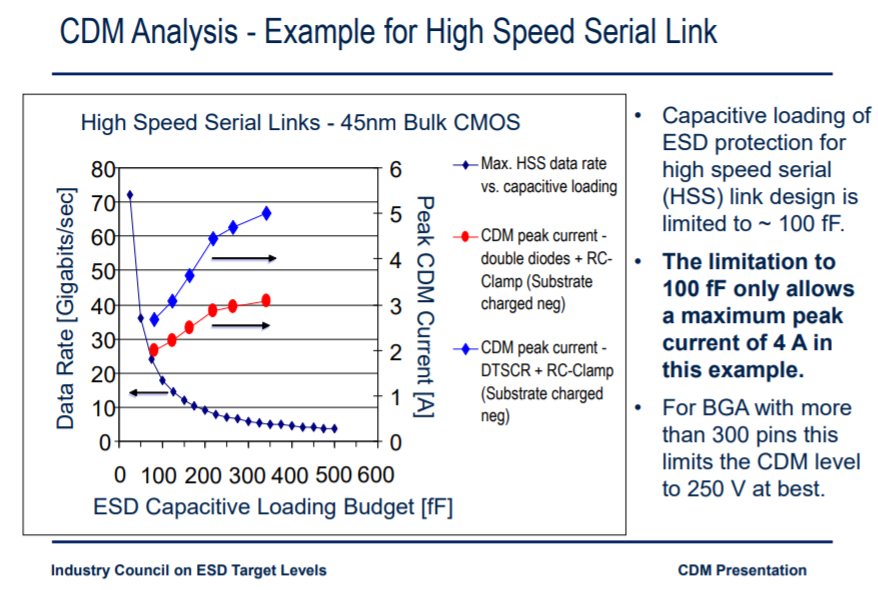

CDM 분석 - 사례, High speed serial link(interface)

High speed serial link 설계를 위한 ESD 보호 회로의 capacitance 는 100fF 이하여야 합니다.

capacitance가 커지면 원하는 speed로 통신하지 못합니다.

capacitance 100fF 제한은 4A의 peak current 전류정도를 감당할 수 있습니다.

300pin 이상 BGA 의 경우 CDM은 최대 250V 수준이 됩니다.

200 ~ 250V 가 달성가능한 실용수준입니다.

안전한 제조를 위한 ESD 제어 관련

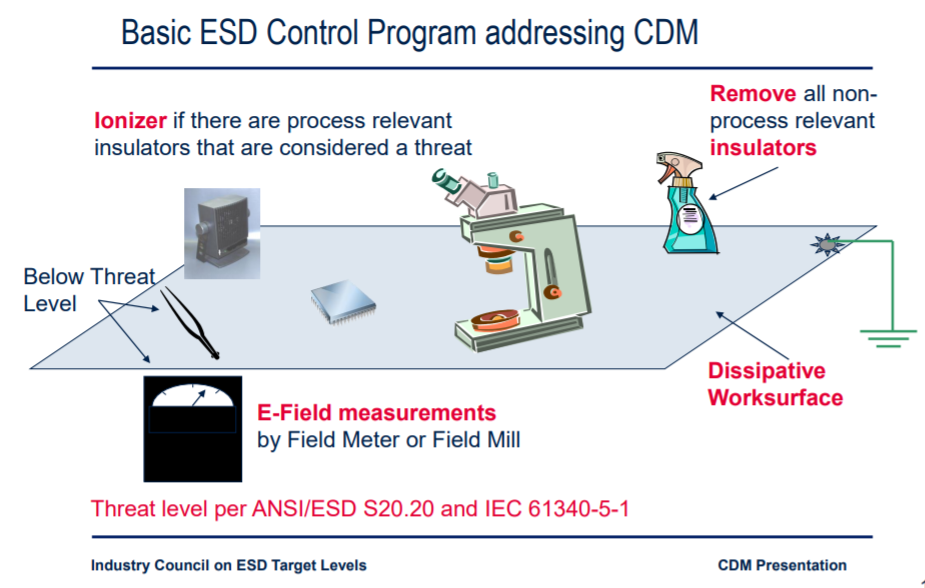

CDM의 경우 HBM 과 마찬가지로, 생산 영역에서의 ESD 제어가 안전한 제조공정의 필수 적인 부분입니다.

CDM 이벤트를 다루는 효과적인 ESD 제어 조치에는 금속기계 부품의 접지, IC와 금속- 금속 접촉 제어 그.리.고 절연체 제어

절연체 제어는 다양한 취급 단계 마다 필요합니다.

위협으로 간주되는 공정 관련 절연체가 있는경우 이온화기.

공정과 관련없는 절연체 제거

작업대 접지

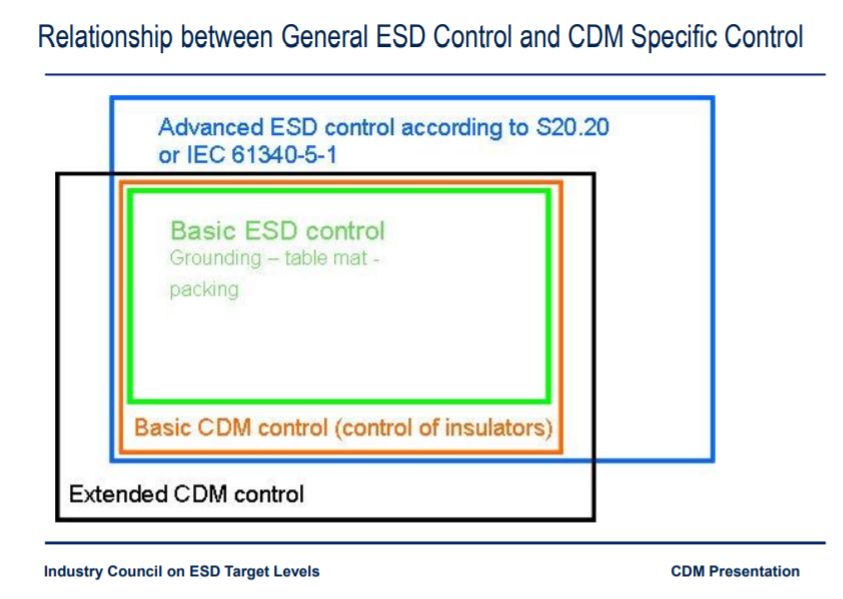

일반적인 ESD 제어와 CDM 특화 제어의 관계

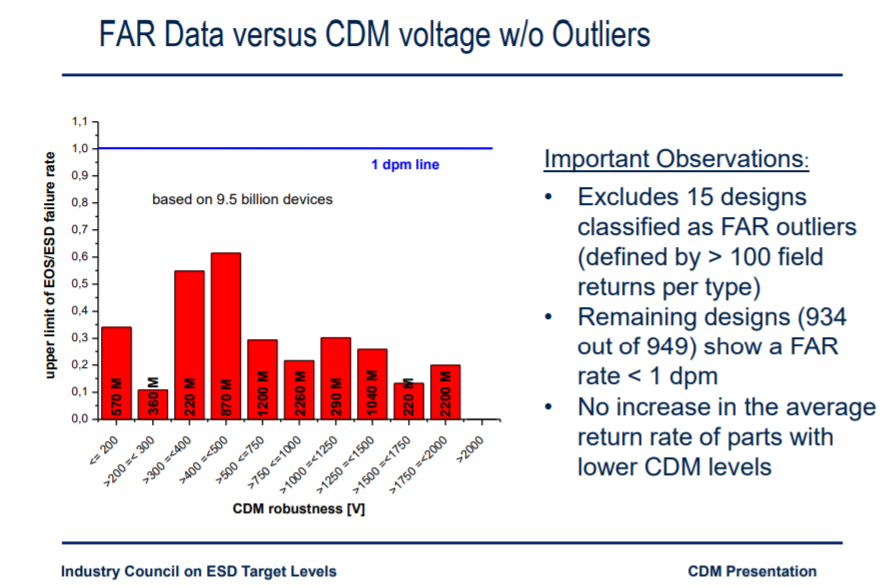

FAR data 분석

110억개 이상의 출하 IC에 대해 다양한 협의회 구성원으로부터 FAR data를 수집했습니다.

IC 공급업체의 취급 및 테스트 불량율, PCB 제조및 최종 고객 불량이 포함됐습니다.

자동차,소비자,메모리 및 개별 제품을 포함하는 949개의 디자인이 포함돼 있습니다.

제시된 데이터는 2003년 부터 2007년 까지 수집 되었습니다.

FAR data versus CDM voltage

중요한 관찰

EOS/ESD 고장률은 CDM robustness와 명확한 상관관계가 보이지 않습니다.

높은 불량율을 가진 몇가지 디자인이 통계를 지배합니다.

높은 불량율을 가진 data를 제거한 data입니다.

낮은 CDM level에서 불량율이 높지 않습니다.

다음편으로 이어집니다.