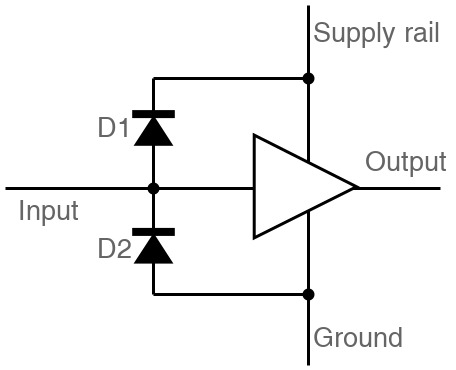

TVS diode란? 외부 stress (ESD, EOS)로 부터 반도체 회로를 보호하기위해 추가하는 부품들은 Current limiter와 Voltage limiter가 있다. ESD로 부터 반도체회로를 보호하기 위해 Power rail에 많이 추가하는 부품이 TVS diode다. TVS diode는 과도 전압(overshooting voltage)을 클램핑해준다. 비슷한 역할을 하는 부품은 바리스터가 있다. 자신이 개발하는 부품이 가격에 민감하면 바리스터도 좋다. 일정 전압 이상이 되면 전류가 증가한다는 점은 제너 다이오드와 같지만 순간적으로 수백 와트 이상의 대전력을 흘려보낼 수 있기 때문에 서지 보호에 활용할 수 있다. 과도 억제 다이오드라고도하는 TVS (Transient Voltage Supp..