첫번째를 못보신분은 여기서부터 따라오세요.

https://tozest.tistory.com/47?category=836576

문답식으로 알아보는 System Level ESD(첫번째)

Sytem이란? System 은 임베디드 IC와 다양한 전자부품으로 구성돼 있다. 소비자,자동차,군사,항공 제품등을 통들어 얘기한다. 쓰이는 곳이 많고, 다양한 환경에서 사용하므로 제어되지 않은 ESD이벤트에 노출될 가..

tozest.tistory.com

System ESD 평가 결과 분류는 어떻게 하는가?

-Pass : 시스템 정상 동작

-Softfail : 자체 회복가능

-외부 개입이 필요한 Softfail (리부팅, Power of/off)

-물리적인 failure

불량유형 분류(제한된 case study로 참고만 할것) 하면?

일반적인 system failure 결과

-Charged Board Events(CBE)

-Cable Discharge Events(CDE)

-Electrical Overstress (EOS)

-IEC System level ESD testing

System level ESD 와 Component level ESD 의 차이

| 분류 | System level ESD - IEC | Component level ESD HBM |

| ESD event 상황 예 |

사람에 충전된 charge가 금속 도구를 통해 System으로 빠져나감

|

사람에 충전된 charge가 피부를 통해 IC(Component)로 빠져 나감

|

| Model | IEC system level ESD | Human Body Model (HBM) |

| 환경 | IEC 61000-4-2 (Powered) ISO 10605 (Unpowered / Powered) | JS-001-2013 (Unpowered only) |

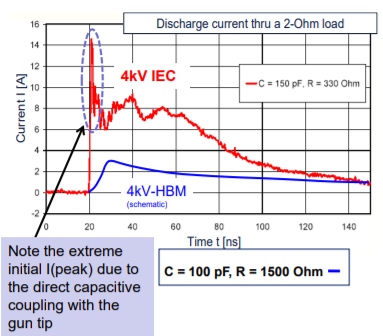

| Peak current | 3.75 A / kV | 0.7 A / kV |

| Typical requirement | 8 KV | 1 KV (Formerly 2kV) |

| Rise time | 0.6 ~ 1 ns | 2 ~ 10 ns |

| Failures | Soft and Hard | Hard |

| Application | PC, Cell phone, Modem, etc… | IC |

| Tester examples | KeyTek Minizap, Noiseken ESS2000 | KeyTek Zapmaster MK2, Oryx |

Waveforem 비교 System level ESD 와 Component HBM

-

System level ESD gun test는 Power가 인가된상태에서 실시한다.

-

Power가 인가된 시스템의 불량유형은 Destructive fail과 Functional / Operational fail이 있다.

Pass/Fail 기준은 무엇인가?

-

HBM/CDM : 물리적인 damage

-

System level ESD : 일시적인 동작오류나 물리적인 damage

Component와 System test결과 상관관계가 있는가?

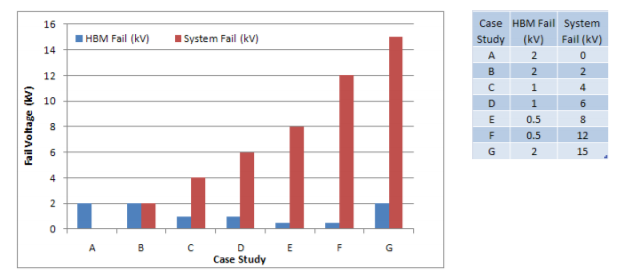

A부터 G group은 HBM과 IEC기반으로 system level평가결과를 표시했다.

결과는 HBM failure 수준과 IEC failure수준사이 관계는 아무 연관성이 없다.

이런 두 test간의 disparity는 test하는 동안, stress waveform이 다르고 test하는 방법이 다르기 때문이다.

둘사이에는 어떤 의존성이 있는가?

HBM과 CDM 개선은 system 보호를 더 어렵게 만든다.

HBM과 CDM 회로 설계는 power가 없다는 가정을 한다.

HBM과 CDM은 softfail을 다루지 않는다.

HBM과 CDM은 외부 소자가 없다고 가정한다.

반면에 System level ESD 강건성은 모든 component와 board design에 영향을 받는다.

IC 단품은 ESD는 하지 않는가?

HBM & CDM test를 한다.

IC업체는 test를 하는데, IC가 ESD 환경을 잘 조정한 상태에서 살아남는지를 확인하기 위해 한다. (굉장히 좁은범위에서 IC를 보증하는것이다.)

결론

component ESD level개선은 system level ESD 성능을 개선할 수 없다.

System 의 ESD 강건함을 얻기 위해서는 이런 차이를 이해하는것에부터 시작해야 한다.

System ESD 강건성을 확보하기 위해선 보드에 있는 보호 소자특성 , 최적화된 보드 신호 경로, component packaging, component의 ESD 수준을 모두 고려해야한다.

함께 읽으면 도움이 되는 글:

2020/03/22 - [ESD engineering] - 문답식으로 알아보는 System Level ESD(첫번째)

2020/03/22 - [ESD engineering] - 문답식으로 알아보는 System Level ESD(두번째)

2020/04/22 - [ESD engineering] - 문답식으로 알아보는 시스템 레벨 ESD/EOS (세번째)

2020/04/25 - [ESD engineering] - 문답식으로 알아보는 시스템 레벨 ESD/EOS (네번째)